低電壓SRAM的重要性-創(chuàng)新互聯(lián)

隨著SOC 技術(shù)的發(fā)展,CMOS 工藝尺寸不斷縮小,芯片集成度越來越高,使得單位面積芯片的功耗不斷提高。近年來,便攜式電子產(chǎn)品如智能手機(jī)、平板電腦、數(shù)碼相機(jī)、智能手環(huán)發(fā)展迅猛,而對(duì)于使用電池的便攜式電子產(chǎn)品,芯片的功耗會(huì)直接影響到電池的使用時(shí)間、使用壽命,功耗逐漸成為大規(guī)模集成電路設(shè)計(jì)中最關(guān)心的問題。

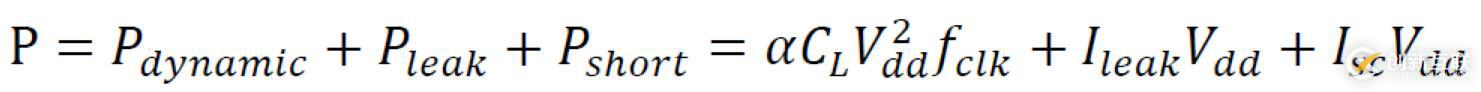

CMOS 集成電路中的功耗由動(dòng)態(tài)功耗、靜態(tài)功耗和短路功耗組成。各個(gè)功耗表達(dá)式如公式所示:

其中,Pdynamic是電路電容充放電產(chǎn)生的動(dòng)態(tài)功耗,與電源電壓成平方關(guān)系;Pleak是靜態(tài)功耗,即漏電流產(chǎn)生的功耗,與電源電壓成一次方關(guān)系;Pshort是電路的短路功耗,產(chǎn)生于NMOS、PMOS 同時(shí)導(dǎo)通的瞬間,同樣與電源電壓成一次方關(guān)系。由此可見降低電源電壓能夠直接有效地降低電路的功耗。

SRAM

的功耗包括動(dòng)態(tài)功耗和靜態(tài)功耗,動(dòng)態(tài)功耗和靜態(tài)功耗所占總功耗的比例不是一成不變的,其比例隨集成電路工藝的發(fā)展而變化。工藝每前進(jìn)一個(gè)節(jié)點(diǎn),MOSFET 漏電流大約增加5 倍。器件特征尺寸的減少,使得靜態(tài)功耗在電路總功耗中所占比例越來越大,同時(shí)也必然引起靜態(tài)泄漏電流的增加。據(jù)統(tǒng)計(jì),在90nm 工藝下,IC 漏電流功耗大約占整個(gè)功耗的1/3,在65nm 工藝下,IC 漏電流功耗已經(jīng)占總功耗的一半以上。由于動(dòng)態(tài)功耗與電源電壓是平方的關(guān)系,靜態(tài)功耗與電源電壓是一次方關(guān)系,降低電源電壓能夠使得動(dòng)態(tài)功耗和靜態(tài)功耗都得到大幅降低。

文章名稱:低電壓SRAM的重要性-創(chuàng)新互聯(lián)

瀏覽地址:http://vcdvsql.cn/article12/csehdc.html

成都網(wǎng)站建設(shè)公司_創(chuàng)新互聯(lián),為您提供自適應(yīng)網(wǎng)站、微信公眾號(hào)、網(wǎng)站收錄、搜索引擎優(yōu)化、品牌網(wǎng)站建設(shè)、企業(yè)網(wǎng)站制作

聲明:本網(wǎng)站發(fā)布的內(nèi)容(圖片、視頻和文字)以用戶投稿、用戶轉(zhuǎn)載內(nèi)容為主,如果涉及侵權(quán)請盡快告知,我們將會(huì)在第一時(shí)間刪除。文章觀點(diǎn)不代表本網(wǎng)站立場,如需處理請聯(lián)系客服。電話:028-86922220;郵箱:631063699@qq.com。內(nèi)容未經(jīng)允許不得轉(zhuǎn)載,或轉(zhuǎn)載時(shí)需注明來源: 創(chuàng)新互聯(lián)

- 怎樣解決Google有害信息的網(wǎng)站提示 2016-04-10

- 百度已經(jīng)正式支持 Google AMP 頁面數(shù)據(jù)提交 2020-09-06

- 為什么你的Google推廣效果不佳? 2016-03-10

- 什么是Google SEO(谷歌優(yōu)化)? 2023-05-05

- 外貿(mào)網(wǎng)站設(shè)計(jì)如何被Google快速收錄 2016-01-13

- 網(wǎng)站優(yōu)化之Google搜索引擎原理 2016-03-04

- Google AMP慶祝其成立三周年,如何開啟。 2019-10-25

- 成都外貿(mào)推廣:充分利用新Google Search Console的7個(gè)步驟 2016-03-01

- Google回歸中國對(duì)SEO們意味著什么? 2016-08-28

- 企業(yè)如何在Google推廣上投放關(guān)鍵字? 2016-06-24

- google優(yōu)化怎樣做才能取得好的排名? 2016-03-10

- 新版Google Fonts,多種字體供網(wǎng)站建設(shè)者免費(fèi)使用 2019-09-26